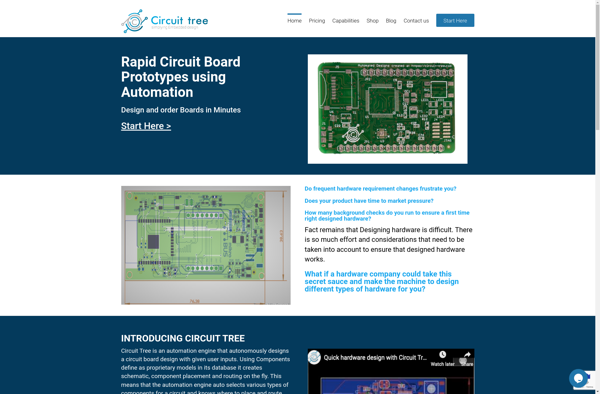

Description: Circuit Tree is an open-source electronics design automation software focused on creating schematics and PCB layouts. It features an intuitive graphical user interface along with powerful tools for schematic capture, PCB layout, autotracing and more.

Type: software

Pricing: Open Source

Description: ModelSim is a digital circuit simulator used for simulating and debugging HDL designs like VHDL, Verilog, and SystemVerilog. It enables functional and timing simulations of RTL designs before synthesis to verify functionality.

Type: software